# JVC SERVICE MANUAL

# DVD DIGITAL CINEMA SYSTEM

# Contents

| 2 |

|---|

| 4 |

| 5 |

| 6 |

|   |

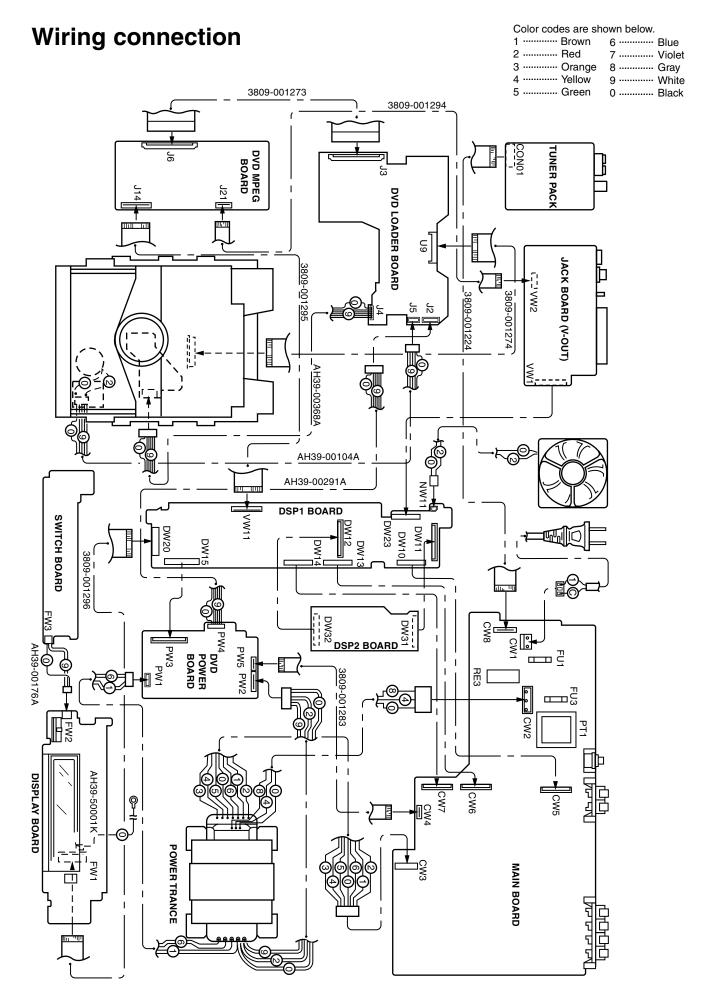

| Wiring connection 1-13           |

|----------------------------------|

| Adjustment method 1-14           |

| Description of major ICs 1-16~34 |

TH-A5R

# -Safety Precautions

- 1. This design of this product contains special hardware and many circuits and components specially for safety purposes. For continued protection, no changes should be made to the original design unless authorized in writing by the manufacturer. Replacement parts must be identical to those used in the original circuits. Services should be performed by qualified personnel only.

- 2. Alterations of the design or circuitry of the product should not be made. Any design alterations of the product should not be made. Any design alterations or additions will void the manufacturer's warranty and will further relieve the manufacture of responsibility for personal injury or property damage resulting therefrom.

- 3. Many electrical and mechanical parts in the products have special safety-related characteristics. These characteristics are often not evident from visual inspection nor can the protection afforded by them necessarily be obtained by using replacement components rated for higher voltage, wattage, etc. Replacement parts which have these special safety characteristics are identified in the Parts List of Service Manual. Electrical components having such features are identified by shading on the schematics and by (A) on the Parts List in the Service Manual. The use of a substitute replacement which does not have the same safety characteristics as the recommended replacement parts shown in the Parts List of Service Manual may create shock, fire, or other hazards.

- 4. The leads in the products are routed and dressed with ties, clamps, tubings, barriers and the like to be separated from live parts, high temperature parts, moving parts and/or sharp edges for the prevention of electric shock and fire hazard. When service is required, the original lead routing and dress should be observed, and it should be confirmed that they have been returned to normal, after re-assembling.

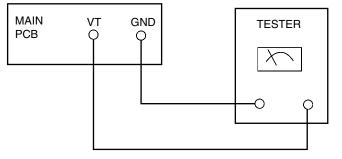

- 5. Leakage currnet check (Electrical shock hazard testing)

After re-assembling the product, always perform an isolation check on the exposed metal parts of the product (antenna terminals, knobs, metal cabinet, screw heads, headphone jack, control shafts, etc.) to be sure the product is safe to operate without danger of electrical shock.

Do not use a line isolation transformer during this check.

Plug the AC line cord directly into the AC outlet. Using a "Leakage Current Tester", measure the leakage current from each exposed metal parts of the cabinet, particularly any exposed metal part having a return path to the chassis, to a known good earth ground. Any leakage current must not exceed 0.5mA AC (r.m.s.).

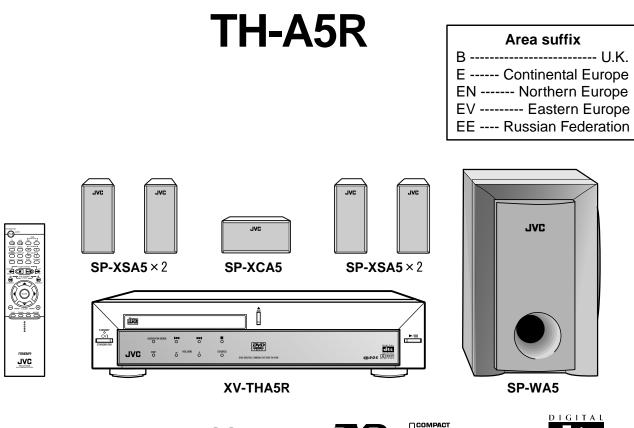

#### Alternate check method

Plug the AC line cord directly into the AC outlet. Use an AC voltmeter having, 1,000 ohms per volt or more sensitivity in the following manner. Connect a 1,500  $\Omega$  10W resistor paralleled by a 0.15 $\mu$ F AC-type capacitor

between an exposed metal part and a known good earth ground. Measure the AC voltage across the resistor with the AC voltmeter.

Move the resistor connection to each exposed metal part, particularly any exposed metal part having a return path to the chassis, and meausre the AC voltage across the resistor. Now, reverse the plug in the AC outlet and repeat each measurement. Voltage measured any must not exceed 0.75 V AC (r.m.s.). This corresponds to 0.5 mA AC (r.m.s.).

# Warning

- 1. This equipment has been designed and manufactured to meet international safety standards.

- 2. It is the legal responsibility of the repairer to ensure that these safety standards are maintained.

- 3. Repairs must be made in accordance with the relevant safety standards.

- 4. It is essential that safety critical components are replaced by approved parts.

- 5. If mains voltage selector is provided, check setting for local voltage.

In regard with component parts appearing on the silk-screen printed side (parts side) of the PWB diagrams, the parts that are printed over with black such as the resistor (--), diode (+-) and ICP (-) or identified by the " $\underline{\wedge}$ " mark nearby are critical for safety.

(This regulation does not correspond to J and C version.)

Burrs formed during molding may be left over on some parts of the chassis. Therefore, pay attention to such burrs in the case of preforming repair of this system.

preforming repair of this system.

# Safety precautions (U.K only) -

- 1. This design of this product contains special hardware and many circuits and components specially for safety purposes. For continued protection, no changes should be made to the original design unless authorized in writing by the manufacturer. Replacement parts must be identical to those used in the original circuits.

- 2. Any unauthorised design alterations or additions will void the manufacturer's guarantee ; furthermore the manufacturer cannot accept responsibility for personal injury or property damage resulting therefrom.

- 3. Essential safety critical components are identified by ( ⚠) on the Parts List and by shading on the schematics, and must never be replaced by parts other than those listed in the manual. Please note however that many electrical and mechanical parts in the product have special safety related characteristics. These characteristics are often not evident from visual inspection. Parts other than specified by the manufacturer may not have the same safety characteristics as the recommended replacement parts shown in the Parts List of the Service Manual and may create shock, fire, or other hazards.

- 4. The leads in the products are routed and dressed with ties, clamps, tubings, barriers and the like to be separated from live parts, high temperature parts, moving parts and/or sharp edges for the prevention of electric shock and fire hazard. When service is required, the original lead routing and dress should be observed, and it should be confirmed that they have been returned to normal, after re-assembling.

# Warning

- 1. Service should be performed by qualified personnel only.

- 2. This equipment has been designed and manufactured to meet international safety standards.

- 3. It is the legal responsibility of the repairer to ensure that these safety standards are maintained.

- 4. Repairs must be made in accordance with the relevant safety standards.

- 5. It is essential that safety critical components are replaced by approved parts.

- 6. If mains voltage selector is provided, check setting for local voltage.

A CAUTION Burrs formed during molding may be left over on some parts of the chassis. Therefore, pay attention to such burrs in the case of preforming repair of this system.

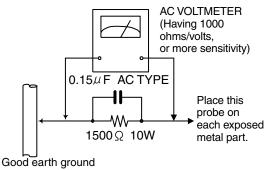

# Important for laser products

#### **1.CLASS 1 LASER PRODUCT**

- **2.DANGER :** Invisible laser radiation when open and inter lock failed or defeated. Avoid direct exposure to beam.

- **3.CAUTION :** There are no serviceable parts inside the Laser Unit. Do not disassemble the Laser Unit. Replace the complete Laser Unit if it malfunctions.

- **4.CAUTION :** The compact disc player uses invisible laserradiation and is equipped with safety switches whichprevent emission of radiation when the drawer is open and the safety interlocks have failed or are de feated. It is dangerous to defeat the safety switches.

- **5.CAUTION :** If safety switches malfunction, the laser is able to function.

- **6.CAUTION :** Use of controls, adjustments or performance of procedures other than those specified herein may result in hazardous radiation exposure.

A CAUTION Please use enough caution not to see the beam directly or touch it in case of an adjustment or operation check.

| VARNING | : Osynlig laserstrålning är denna del är öppnad   | ADVARSEL : Usynlig laserstråling ved åbning , når |

|---------|---------------------------------------------------|---------------------------------------------------|

|         | och spårren är urkopplad. Betrakta ej strålen.    | sikkerhedsafbrydere er ude af funktion. Undgå     |

| VARO    | : Avattaessa ja suojalukitus ohitettaessa olet    | udsættelse for stråling.                          |

|         | alttiina näkymättömälle lasersäteilylle.Älä katso | ADVARSEL : Usynlig laserstråling ved åpning,når   |

|         | säteeseen.                                        | sikkerhetsbryteren er avslott. unngå utsettelse   |

|         |                                                   | for stråling.                                     |

# **Preventing static electricity**

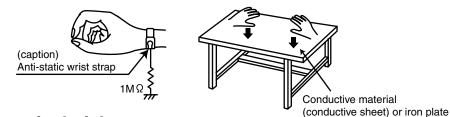

# 1. Grounding to prevent damage by static electricity

Electrostatic discharge (ESD), which occurs when static electricity stored in the body, fabric, etc. is discharged, can destroy the laser diode in the traverse unit (optical pickup). Take care to prevent this when performing repairs.

# 2. About the earth processing for the destruction prevention by static electricity

Static electricity in the work area can destroy the optical pickup (laser diode) in devices such as CD players. Be careful to use proper grounding in the area where repairs are being performed.

#### 2-1 Ground the workbench

Ground the workbench by laying conductive material (such as a conductive sheet) or an iron plate over it before placing the traverse unit (optical pickup) on it.

#### 2-2 Ground yourself

Use an anti-static wrist strap to release any static electricity built up in your body.

# 3. Handling the optical pickup

- 1. In order to maintain quality during transport and before installation, both sides of the laser diode on the replacement optical pickup are shorted. After replacement, return the shorted parts to their original condition. (Refer to the text.)

- 2. Do not use a tester to check the condition of the laser diode in the optical pickup. The tester's internal power source can easily destroy the laser diode.

# 4. Handling the traverse unit (optical pickup)

- 1. Do not subject the traverse unit (optical pickup) to strong shocks, as it is a sensitive, complex unit.

- 2. Cut off the shorted part of the flexible cable using nippers, etc. after replacing the optical pickup. For specific details, refer to the replacement procedure in the text. Remove the anti-static pin when replacing the traverse unit. Be careful not to take too long a time when attaching it to the connector.

- 3. Handle the flexible cable carefully as it may break when subjected to strong force.

- 4. It is not possible to adjust the semi-fixed resistor that adjusts the laser power. Do not turn it.

# Attention when traverse unit is decomposed

\*Please refer to "Disassembly method" in the text for pick-up and how to detach the substrate.

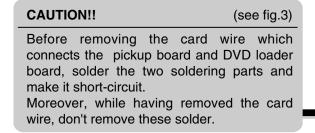

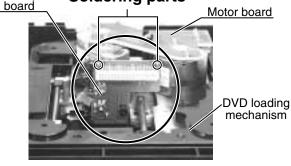

1. Solder is put up before the card wire is removed from connector DVD mechanism assembly (bottom side) (These two points are Short land soldered respectively, on the pick up board as shown in and are made to **DVD** loading Figure. short-circuit) mechanism (When the wire is removed without putting up solder, the CD pick-up assembly might destroy.) 2. Please remove solder after Connector connecting the card wire with when you install picking up Pick up board in the substrate. Card wire

# **Disassembly method**

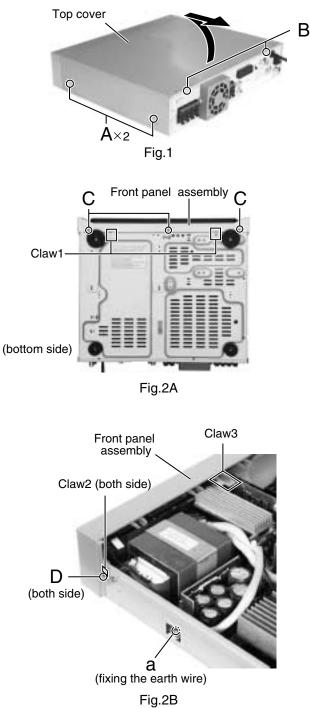

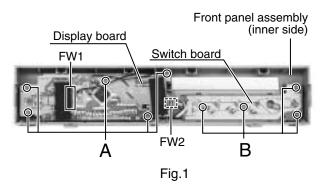

#### ■ Removing the top cover (See Fig.1)

- 1. Remove the four screws **A** attaching the top cover on the both sides of the body.

- 2. Remove the two screws **B** on the back of the body.

- 3. Remove the top cover from behind in the direction of the arrow while pulling both sides outward.

#### Removing the front panel assembly (See Fig.2A, 2B and 3)

- Prior to performing the following procedure, remove the top cover.

- 1. Remove the one screw **a** and remove the earth wier.

- 2. Remove the three screws **C** attaching the front panel assembly on the bottom of the body.

- 3. Remove the two screws **D** attaching the front panel assembly on the both sides of the body.

- 4. Remove the claw1, claw2 and claw3, and detach the front panel assembly toward the front.

- 5. Disconnect the card wire from the connector DW20 on the DSP board.

#### ■ Removing the power cord (See Fig.4)

- Prior to performing the following procedure, remove the top cover.

- 1. Cut off the tie band, if needed.

- 2. Disconnect the power cord from the connector CW1 on the main board and pull up the cord stopper upward.

CW1

Tie band

Fig.4

Notes: The power cord is exchangeable.

Rear panel

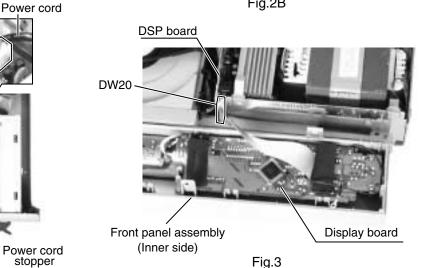

## Removing the DVD mechanism assembly (See Fig.5 and 6)

- Prior to performing the following procedure, remove the top cover.

- 1. Disconnect the card wire from the connector J14 and J21 on the DVD MPEG board.

- 2. Remove the two screws **E** attaching the DVD mechanism assembly and pull up with drawing out.

- 3. Disconnect the harness from the connector J2 on the DVD loader board.

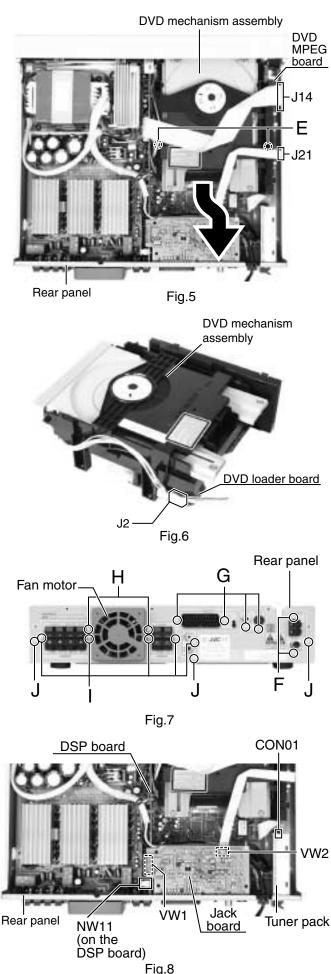

- ■Removing the rear panel (See Fig.7 and 8)

- Prior to performing the following procedure, remove the top cover and power cord.

- 1. Disconnect the harness from the connector NW11 on the DSP board.

- 2. Remove the two screws **F**, four screws **G**, and five screws **I** attaching the each boards to the rear panel.

- 3. Remove the three screws **J** attaching the rear panel on the back of the body.

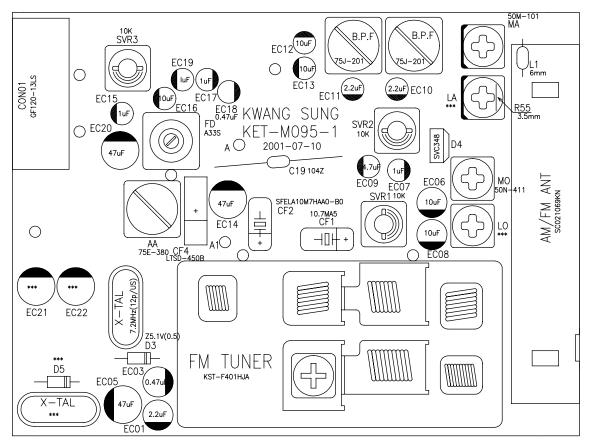

## Removing the tuner pack (See Fig.7 and 8)

- Prior to performing the following procedure, remove the top cover.

- 1. Disconnect the card wire from the connector CON01 on the tuner pack.

- 2. Remove the two screws **F** attaching the tuner pack to the rear panel.

## ■ Removing the jack board (See Fig.7 and 8)

- Prior to performing the following procedure, remove the top cover.

- 1. Disconnect the card wire from the connector VW2 on the jack board.

- 2. Remove the four screws **G** attaching the jack board to the rear panel.

- 3. Disconnect the connector VW1 on the jack board and pull up the jack board.

#### Removing the fan motor (See Fig.7 and 8)

- Prior to performing the following procedures, remove the top cover .

- 1. Disconnect the harness from the connector NW11 on the DSP board .

- 2. Removing the two screws **H** attaching the fan motor on the rear panel.

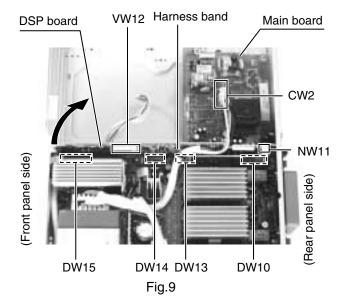

# ■ Removing the DSP board (See Fig.9)

- Prior to performing the following procedure, remove the top cover, front panel assembly and jack board.

- 1. Untied the harness band and disconnect the harness from the connector CW2 on the main board.

- 2. Disconnect the harness from the connector NW11 on the DSP board.

- 3. Disconnect the card wire from the connector VW12 on the DSP board.

- 4. Pull up the DSP board from the front side upwards disconnecting the connector DW10, DW13, DW14 and DW15.

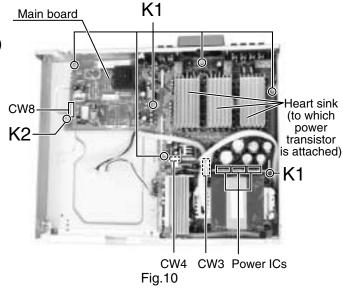

## ■ Removing the main board (See Fig.10)

- Prior to performing the following procedure, remove the top cover, front panel assembly, DVD mechanism assembly, jack board and DSP board.

- 1. Disconnect the card wire from the connector CW4 and CW8 on the main board.

- 2. Disconnect the harness from the connector CW3 on the main board.

- 3. Remove the five screws I attaching the speaker terminals and jack to the rear panel (see fig.7).

- 4. Remove the six screws **K1** (short) and one screw **K2** (long) attaching the main board.

- 5. When the rear panel is not removed, pull up the main board from front side.

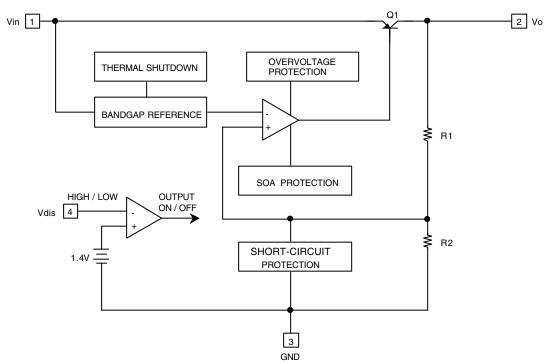

# Removing the power transistor & power IC (See Fig.10 and 11)

- Prior to performing the following procedure, remove the top cover, front panel assembly, DVD mechanism assembly, jack board, DSP board and main board.

- 1. After removing the solder part soldered to the main board, remove each screw and remove the heat sink from Power transistor.

- 2. After removing the solder part soldered to the main board, remove each screw and remove the heat sink from Power IC.

(Each power transistor is fixed)

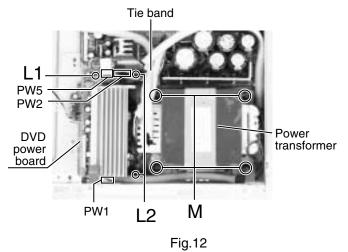

#### Removing the DVD power board

#### (See Fig.12)

- Prior to performing the following procedure, remove the top cover, front panel assembly and DSP board.

- 1. Disconnect the harness and card wire from the connector PW1, PW2 and PW5 on the DVD power board.

- 2. Remove the one screw L1 (short) and two screws L2 (long) attaching the DVD power board.

- Removing the power transformer (See Fig.12)

- Prior to performing the following procedure, remove the top cover.

- 1. Cut off the tie band fixing the harness, if needed.

- Disconnect the harness from the connector CW2 on the main board (see fig.9) and PW1, PW2 on the DVD power board.

- 3. Remove the four screws **M** attaching the power transformer.

# <Front panel assembly section>

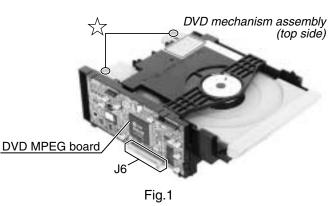

#### Removing the display board & switch board (See Fig.1 and 2)

• Prior to performing the following procedure, remove the top cover and the front panel assembly.

- 1. Disconnect the card wire from the connector FW1 on the display board.

- 2. Remove the five screws **A** attaching the display board on the inner of the front panel assembly.

- 3. Remove the four screws **B** attaching the switch board on the inner of the front panel assembly.

- 4. Disconnect the harness from connector FW2 on the display board, if needed.

#### Removing the front window

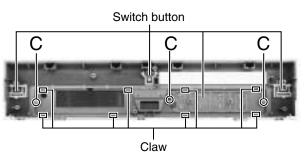

# (See Fig.2 and 3) Prior to performing the following procedure, remove the top cover, front panel assembly, display board and switch board.

- 1. Remove the switch buttons, if needed.

- 2. Remove the three screws **C** attaching the front window on the front panel.

- 3. Remove the eight claws fixing the front window on the front panel.

Front panel assembly (front side)

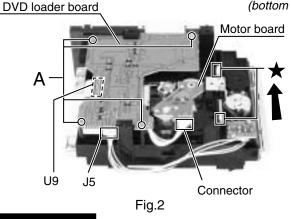

# <DVD mechanism assembly section> Removing the DVD loader board (See Fig.1 to 3)

- · Prior to performing the following procedure, remove the top cover and DVD mechanism assembly.

- 1. Disconnect the card wire from the connector J6 on the DVD MPEG board.

- 2. Disconnect the harness from the connector on the motor board.

- 3. Disconnect the harness from the connector J5 on the DVD loader board.

- 4. Remove the four screws A attaching the DVD loader board to DVD mechanism assembly.

5. Disconnect the card wire from the connector U9 on the DVD loader board.

#### ONE POINT

#### How to eject the DVD tray manually

(see fig.2)

The white lever of the  $\bigstar$  mark is moved in the direction of the arrow. Then, the tray will be opened.

Moreover, the tray is separable from a DVD mechanism assembly by removing two screws of the mark (see fig.1) and drawing out the tray.

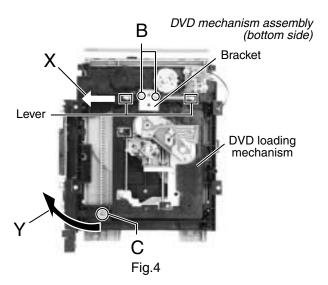

# Removing the DVD loading mechanism (See Fig.4)

- · Prior to performing the following procedure, remove the top cover, DVD mechanism assembly and DVD loader board.

- 1. Remove the two screws **B** and remove the bracket.

- 2. Remove the one screw C fixing the DVD loading mechanism.

- 3. Move the lever in the direction of the arrow X.

- 4. Remove the DVD loading mechanism from the DVD mechanism assembly by moving it in the direction of the arrow Y.

DVD mechanism assembly (bottom side)

Pick up Soldering parts

Fig.3

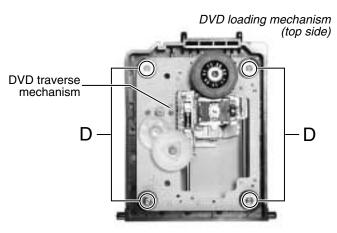

## Removing the DVD traverse mechanism (See Fig.5)

- Prior to performing the following procedure, remove the top cover, DVD mechanism assembly, DVD loader board and DVD loading mechanism.

- 1. Remove the four screws **D** attaching the DVD traverse mechanism to DVD loading mechanism.

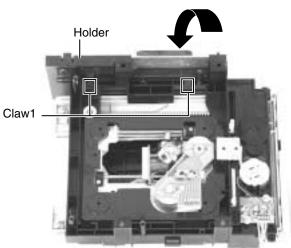

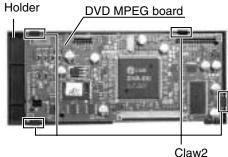

#### Removing the holder & DVD MPEG board (See Fig.6 and 7)

- Prior to performing the following procedure, remove the top cover, DVD mechanism assembly and DVD loader board.

- 1. Remove the two claws1, and remove the holder from the DVD mechanism assembly as it is pushed down.

Notes: When removing only the DVD MPEG board, it is not necessary to remove this holder.

2. Remove the four claws2 and remove the DVD MPEG board from the holder.

DVD mechanism assembly Fig.6 (bottom side)

Fig.7

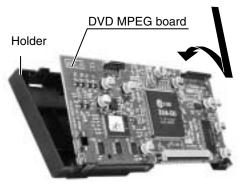

#### ONE POINT

When inserting DVD MPEG board in holder. (see fig.8)

Insert in after uniting with a lower claws, when inserting DVD MPEG board in holder.

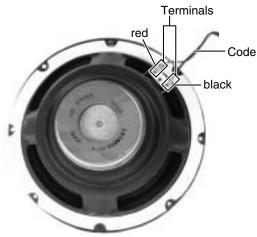

# <Speaker section> [SP-XSA5 / Satellite speaker]

It is exchange in a unit.

# [SP-XCA5 / Center speaker]

It is exchange in a unit.

# [SP-WA5 / Woofer]

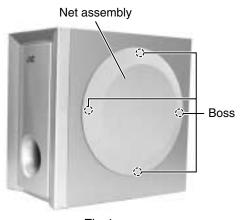

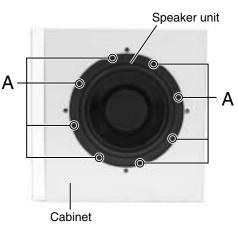

Removing the speaker unit

(See Fig.1 to 3)

1. Remove the four bosses and remove the net assembly.

Notes: It will be good to use the tool with a flat tip, since it is hard to remove. Please take care not to damage the cabinet at this time.

- 2. Remove the eight screws **A** attaching the speaker unit to cabinet.

- 3. Disconnect the code from the two terminals of the speaker unit.

Fig.2

Speaker unit (reverse side)

# TH-A5R

# Adjustment method

# 1. Tuner

\*Adjustment Location of Tuner PCB

| ITEAM               | AM(MW) OSC<br>Adjustment | AM(MW) RF<br>Adjustment   |

|---------------------|--------------------------|---------------------------|

| Received FREQ.      | 522~1629 KHz             | 603 KHz                   |

| Adjustment<br>point | МО                       | МА                        |

| Output              | 1~7.0V                   | Maximum<br>Output(Fig1-1) |

Fig 1-1 OSC Voltage

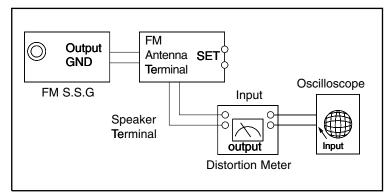

| FM THD Adjustment                               |                  |  |

|-------------------------------------------------|------------------|--|

| SSG FREQ.                                       | 98 MHz           |  |

| Adjustment<br>point<br>(FD)                     | FM DETECTOR COIL |  |

| Output                                          | 60 dB            |  |

| Minumum Distortion (0.4% below)<br>(Figure 1-2) |                  |  |

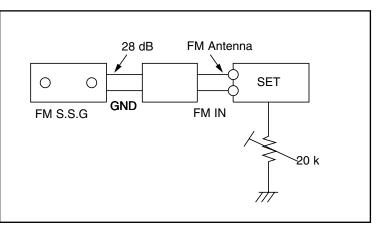

| FM Search Level Adjustment                                  |                                       |  |  |  |

|-------------------------------------------------------------|---------------------------------------|--|--|--|

| SSG FREQ.                                                   | 98 MHz                                |  |  |  |

| Adjustment<br>point<br>(SVR3)                               | BEACON<br>SENSITIVITY<br>SEMI-VR(20K) |  |  |  |

| Output                                                      | 28 dB( dB)                            |  |  |  |

| Adjust SVR1 so that "TUNED" of FL T is lighted (Figure 1-3) |                                       |  |  |  |

\*Adjust FM S.S.G level to 28dB

Figure1-3 FM Auto Search Level Adjustment

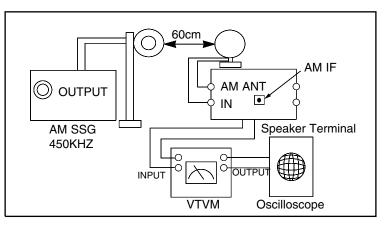

| AM(MW) I.F Adjustment       |         |  |  |

|-----------------------------|---------|--|--|

| SSG FREQ.                   | 450 kHz |  |  |

| Frequency                   | 522 kHz |  |  |

| Adjustment point AA         |         |  |  |

| Maximum output (Figure 1-4) |         |  |  |

Figure1-4 AM I.F Adjustment

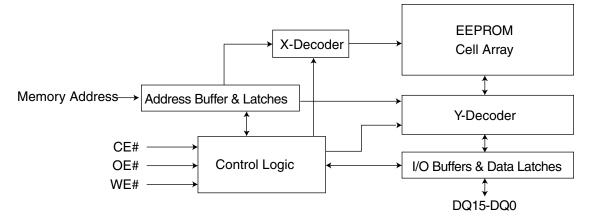

# **Description of major ICs**

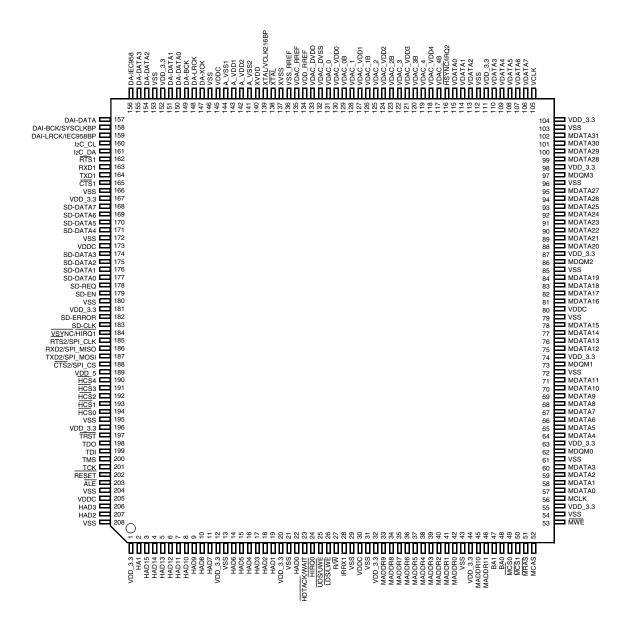

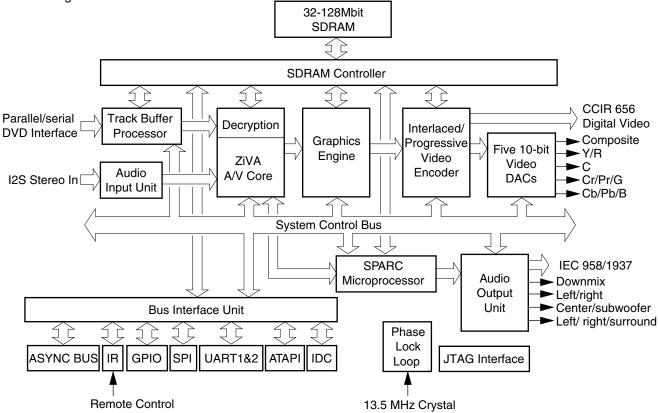

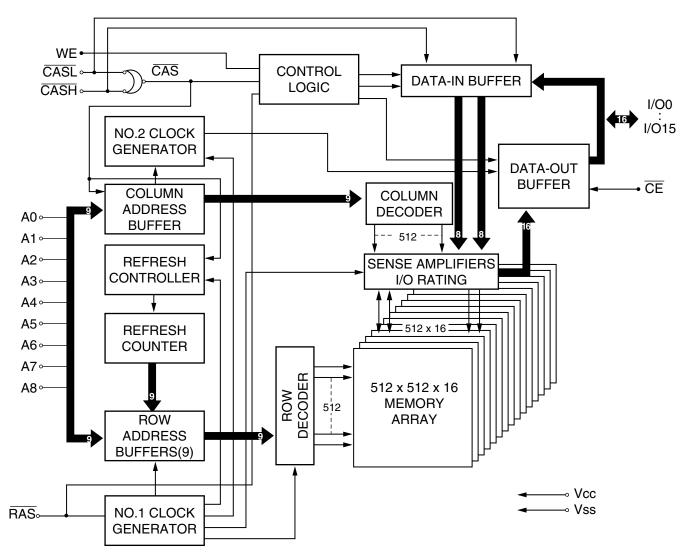

# ■ ZiVA-5 (U8) : DVD controller

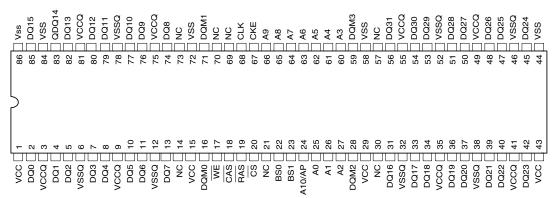

1. Pin layout

2. Pin function

|           | Name               | Pin No. | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------|--------------------|---------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | RESET              | 202     | I                 | Active Low Reset. Assert for at least 5-milliseconds in the presence of clock to reset the entire chip.                                                                                                                                                                                                                                                                                          |

| es        | VCLK               | 105     | I/O               | Video clock that outputs 27 MHz.                                                                                                                                                                                                                                                                                                                                                                 |

| ervice    | XOUT               | 138     | 0                 | Crystal output. When the internal DCXO is used, a 13.5 MHz crystal should be con-nected between this pin and the XIN pin.                                                                                                                                                                                                                                                                        |

| System Se | XIN/bypass clk_216 | 139     | I                 | Crystal input. When the internal DCXO is used, a 13.5 MHz crystal should<br>be con-nected between this pin and the XOUT pin. When an external<br>oscillator or VCXO is used, its output should be connected to this pin.<br>When configured for an external bypass clock, a 216 MHz clock should be<br>connected to this pin. The frequency of an external VCXO can be either 27<br>or 13.5 MHz. |

(1/4)

1. I - input, O - output, OD - open drain, PU - requires external pull-up resistor.

|                          | Nama                 | Din Na                               | <b>T</b>                              | (2/4)                                                                               |

|--------------------------|----------------------|--------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------|

|                          | Name                 | Pin No.                              | Type <sup>1</sup>                     | Description                                                                         |

|                          | VNW                  | 189                                  | Power                                 | 5-V supply voltage for 5V-tolerant I/O signals.                                     |

|                          | VDDP                 | 12, 20, 111, 152, 167, 181, 196      | Power                                 | 3.3-V supply voltage for I/O signals                                                |

| _                        | VDD25                | 32, 44, 55, 63, 74, 87, 98, 104      | Power                                 | 3.3-V supply voltage for SDRAM I/O signals                                          |

|                          | XVDD                 | 140                                  |                                       | 3.3V Crystal infterface power                                                       |

|                          | VDD                  | 30, 80, 145, 173, 205                | Power                                 | 1.8-V suply voltage for core logic                                                  |

| Ground                   | VDD_VDAC[4:0]        | 118, 121, 124, 127, 130              | Power                                 | Analog Video DAC Power                                                              |

| 5                        | VDAC_DVDD            | 133                                  |                                       | 3.3V Digital supply for 5 DACs                                                      |

|                          | A_VDD[2:1]           | 142, 143                             |                                       | 3.3-V Analog PLL Power                                                              |

| a                        | VDAC REFVDD          | 134                                  | Power                                 | 3.3V Analog Video Reference Voltage                                                 |

| ē                        | GNDP                 | 13, 21, 112, 153, 166, 180, 195, 208 | Ground                                | Ground for I/O signals                                                              |

| LOWEL                    | GND                  | 29, 79, 146, 172, 204                |                                       | Ground for core logic                                                               |

| ר                        | GND25                | 31, 43, 54, 61, 72, 85, 96, 103      |                                       | Ground for SDRAM I/O signals                                                        |

|                          | VDAC_DVSS            | 132                                  |                                       | Digital VSS for DACs                                                                |

|                          | AVSS[2:1]            | 141, 144                             |                                       | Analog PLL Ground                                                                   |

|                          |                      |                                      | Cround                                |                                                                                     |

|                          | VDAC_REFVSS          | 136                                  |                                       | Video Analog Ground                                                                 |

|                          | XVSS                 | 137                                  | Ground                                | Crystal interface ground                                                            |

|                          | HCS[4:2]/GPIO[41:43] | 190-192                              | 0                                     | Host chip select. Host asserts HCS to select the controller for a read or           |

|                          |                      |                                      |                                       | write opera-tion. The falling edge of this signal triggers the read or write        |

|                          |                      |                                      |                                       | operation. General Purpose I/Os 41, 42, and 43, respectively.                       |

|                          | HCS[1:0]             | 193, 192                             |                                       | Host chip select. Host asserts HCS to select the controller for a read or           |

|                          |                      |                                      |                                       | write opera-tion. The falling edge of this signal triggers the read or write        |

|                          |                      |                                      |                                       | operation.                                                                          |

|                          | HA[3:1]              | 206, 207, 2                          | I/O                                   | Host (muxed address) address bus. 3-bit address bus selects one of eigh             |

|                          |                      |                                      |                                       | host inter-face registers. These signals are not muxed in ATAPI master              |

| Ņ                        |                      |                                      |                                       | mode.                                                                               |

| U                        | HA[15:0]             | 3-11, 14-19, 22                      | 1/0                                   | HA[15:0] is the 16-bit (muxed address and data) bi-directional host data            |

| <b>HOST INTERTACE</b>    | HA[15.0]             | 3-11, 14-19, 22                      | 1/0                                   |                                                                                     |

|                          |                      |                                      |                                       | bus through which the host writes data to the decoder Code FIFO. MSB of             |

| ñ                        |                      |                                      |                                       | the 32-bit word is writ-ten first. The host also reads and writes the decode        |

| Ē                        |                      |                                      |                                       | internal registers and local SDRAM/ROM via HA[7:0]. These signals are               |

|                          | l                    |                                      |                                       | not muxed for ATAPI master mode.                                                    |

|                          | HDTACK/WAIT          | 23                                   | I/OD                                  | Host Data Transfer Acknowledge.                                                     |

|                          | HIRQO                | 24                                   | I/O                                   | Host interrupt. Open drain signal, must be pulled-up via 4.7k $\Omega$ to 3.3 volts |

|                          |                      |                                      |                                       | Driven high for 10 ns before tristate.                                              |

|                          | HUDS/UWE             | 25                                   | I/O                                   | Host Upper Data Strobe. Host high byte data, HA[15:8], is valid when this           |

|                          | I IODO/OWE           | 25                                   | "                                     | pin is active.                                                                      |

|                          | HLDS/LWE             | 26                                   | I/O                                   | Host Lower Data Strobe. Host low byte data, HA[7:0], is valid when this pir         |

|                          |                      | 20                                   | "0                                    |                                                                                     |

|                          |                      |                                      |                                       | is active.                                                                          |

|                          |                      | 27                                   | I/O                                   | Read/write strobe                                                                   |

|                          | ALE                  | 203                                  | 1/0                                   | Address latch enable                                                                |

|                          | MCS[1:0]             | 50, 49                               | 0                                     | Memory chip select.                                                                 |

|                          | MCAS                 | 52                                   | 0                                     | Active LOW SDRAM Column Address Strobe.                                             |

| ñ                        | MRAS                 | 51                                   | 0                                     | Active LOW SDRAM Row Address Strobe.                                                |

| SURAM INTELIACE          | MDQM[3:0]            | 97, 86, 73, 62                       | 0                                     | These pins are the bytes masks corresponding to MD[7:0], [15:8], [23:16]            |

| Ð                        |                      |                                      |                                       | and [31:24]. They allow for byte reads/writes to SDRAM.                             |

| Ē                        | MA[11:0]             | 46, 45, 33-42                        | 0                                     | SDRAM Address                                                                       |

|                          | MD[31:0]             | 102-99, 95-88, 84-81,                | I/O                                   | SDRAM Data                                                                          |

|                          |                      | 78-75, 71-64, 60-57                  |                                       |                                                                                     |

| Š                        | MWE                  | 53                                   | 0                                     | SDRAM Write Enable. Specifies transaction to SDRAM: read (=1) or                    |

|                          |                      |                                      |                                       |                                                                                     |

|                          |                      |                                      | · · · · · · · · · · · · · · · · · · · | write (=0)                                                                          |

|                          |                      | 56                                   | 0                                     | SDRAM Clock                                                                         |

|                          | BA[1:0]              | 47, 48                               | 0                                     | SDRAM bank select                                                                   |

|                          | HSYNC/HIRQ2/         | 116                                  | I/O                                   | Horizontal sync. The decoder begins outputting pixel data for a new                 |

|                          | GPIO1[9]             |                                      |                                       | horizontal line after the falling (active) edge of HSYNC.                           |

| 3                        |                      |                                      |                                       | Host Interrupt Request 2                                                            |

| 3                        |                      |                                      |                                       | General Purpose I/O 9                                                               |

| 5                        | VCLK                 | 105                                  | I/O                                   | Video clock. Clocks out data on input. VDATA[7:0].                                  |

| 2                        |                      |                                      |                                       | Clock is typically 27 MHz.                                                          |

| 2                        | VDATA[7:0]/GPIO[1:7] | 106-110, 113-115                     | I/O                                   | Video data bus. Byte serial CbYCrY data synchronous with VCLK. At                   |

|                          |                      |                                      |                                       | powerup, the decoder does not drive VDATA. During boot-up, the                      |

| é                        |                      |                                      |                                       | decoder uses configuration parameters to drive or 3-state VDATA.                    |

| Ugital video inpuroutput |                      |                                      |                                       | General Purpose I/Os [1:7]                                                          |

| 5                        |                      | 104                                  | 1/0                                   |                                                                                     |

| 5                        | VSYNC/HIRQ1/         | 184                                  | 1/0                                   | Vertical sync. Bi-directional, the decoder outputs the top border of a new          |

| 5                        | GPIO36               |                                      |                                       | field on the first HSYNC after the falling edge of VSYNC. VSYNC can                 |

|                          |                      |                                      |                                       | accept vertical synchroni-zation or top/bottom field notification from an           |

|                          |                      |                                      |                                       | external source. (VSYNC HIGH = bot-tom field. VSYNC LOW = Top field                 |

|                          |                      |                                      |                                       | Active Low Host Interrupt Pin                                                       |

|                          |                      |                                      |                                       |                                                                                     |

1. I - input, O - output, OD - open drain, PU - requires external pull-up resistor.

#### 2. Pin function

|                 | SDDATA[7]/VDATA2[7]<br>/HDMARQ/GPIO24 | 168                     | Type <sup>1</sup> | Description<br>Compressed data from DVD DSP. Bit 7. In parallel mode, bit 7 is the first |

|-----------------|---------------------------------------|-------------------------|-------------------|------------------------------------------------------------------------------------------|

|                 |                                       |                         |                   | Compressed data norm DVD DSI . Dit 7. In parallel mode, bit 7 is the lifst               |

|                 |                                       |                         |                   | (earliest in time) bit in the bitstream, while bit 0 is the last bit.                    |

|                 |                                       |                         |                   | Video Data Bus 2, Bit 7                                                                  |

|                 |                                       |                         |                   | Host DMA Request                                                                         |

|                 |                                       |                         |                   | General Purpose I/O 24                                                                   |

|                 | SDDATA6/VDATA2[6]                     | 169                     |                   | Compressed data from DVD DSP. Bit 6.                                                     |

| 0               | /HXCVR_EN/GPIO25                      |                         |                   | Video Data Bus 2, Bit 6                                                                  |

| a               | _                                     |                         |                   | ATAPI Transceiver Enable                                                                 |

| l oo h          |                                       |                         |                   | General Purpose I/O 25                                                                   |

| Õ               | SDDATA5/VDATA2[5]                     | 170                     |                   | Compressed data from DVD DSP. Bit 5.                                                     |

| l fa            | HDMACK/GPIO26                         |                         |                   | Video Data Bus 2, Bit 5                                                                  |

| Interface       |                                       |                         |                   | Host DMA Acknowledge                                                                     |

|                 |                                       |                         |                   | General Purpose I/O 26                                                                   |

| Serial CD       | SDDATA4/VDATA2[4]/                    | 171                     |                   | Compressed data from DVD DSP. Bit 4.                                                     |

| a               | GPIO27                                |                         |                   | Video Data Bus 2, Bit 4                                                                  |

| اق ا            |                                       |                         |                   | General Purpose I/O 27                                                                   |

| 5               | SDDATA3/                              | 174                     |                   | Compressed data from DVD DSP. Bit 3.                                                     |

| اما             | VDATA2[3]/GPIO28                      |                         |                   | Video Data Bus 2, Bit 3                                                                  |

| <u> </u>        |                                       |                         |                   | General Purpose I/O 28                                                                   |

| 121             | SDDATA2/                              | 175                     |                   | Compressed data from DVD DSP. Bit 2.                                                     |

|                 | VDATA2[2]/GPIO29                      | -                       |                   | Video Data Bus 2, Bit 2                                                                  |

| ∎               |                                       |                         |                   | General Purpose I/O 29                                                                   |

| ara             | SDDATA1/                              | 176                     |                   | Compressed data from DVD DSP. Bit 1.                                                     |

| ۱۳              | VDATA2[1]/GPIO30                      |                         |                   | Video Data Bus 2, Bit 1                                                                  |

|                 |                                       |                         |                   | General Purpose I/O 30                                                                   |

|                 | SDDATA0/                              | 177                     |                   | In serial mode, bit 0 should be used as the input, with the unused bits                  |

|                 | VDATA2[0]/GPIO31                      |                         |                   | either used as GPIOs or tied to ground.                                                  |

|                 |                                       |                         |                   | Video Data Bus 2, Bit 0                                                                  |

|                 |                                       |                         |                   | General Purpose I/O 31                                                                   |

|                 | SDCLK                                 | 183                     | 1                 | Data clock. The maximum frequency is 25 MHz for parallel mode, and                       |

|                 |                                       |                         |                   | ???? MHz for serial mode. The polarity of this signal is programmable.                   |

|                 | SDERROR                               | 182                     |                   | Error in input data. This signal carries the error bit associated with the               |

|                 |                                       |                         |                   | channel data type (if set, the byte is ccorrupted).                                      |

|                 | SDEN/GPIO33                           | 179                     | ·····             | Data enable. Assertion indicates that data on SDDATA[7:0] is valid.                      |

|                 |                                       |                         |                   | The polarity of this signal is programmable.                                             |

|                 |                                       |                         |                   | General Purpose I/O [33]                                                                 |

|                 | SDREQ/GPIO32                          | 178                     | 0                 | Bitstream request. controller asserts SDREQ to indicate that the bitstream               |

|                 |                                       |                         |                   | input buffer has available space.                                                        |

|                 |                                       |                         |                   | General Purpose I/O 32                                                                   |

| ⊢ †             | VDAC_[4B:0B]                          | 117, 120, 123, 126, 129 | Analog O          | Video DAC Bias Bits[4:0]                                                                 |

| I h             |                                       | 119                     | Analog O          | DAC video output format: R, V, C, or CVBS. Macrovision encoded.                          |

| ا <u>ک</u> ا    | VDAC_4<br>VDAC_3V<br>DAC_2            | 122                     | Analog O          | DAC video output format: B, U, C, or CVBS. Macrovision encoded.                          |

| 1 H             | DAC 2                                 | 125                     |                   | DAC video output format: G or Y. Macrovision encoded.                                    |

|                 | VDAC_1                                | 128                     | Analog O          | DAC video output format: C. Macrovision encoded.                                         |

|                 | VDAC_0                                | 131                     | Analog O          | DAC video output format: CVBS or Y. Macrovision encoded.                                 |

| اچا             | VDAC_REF                              | 135                     | Analog I          | Video DACs Reference Resistor. Connecting to pin 136 through                             |

| <b>D</b>        |                                       | 100                     | /                 | a 1.18K+/- 1% resis-tor is required.                                                     |

| Analog Video    | VCLK                                  | 105                     | I/O               | System clock that drives internal PLLs. ZiVA-5 27-MHz TTL oscillator.                    |

| ا¥              |                                       |                         |                   | (See descrip-tion of VCLK for Digital Video Output.) Also optional video                 |

| 1               |                                       |                         |                   | clock for internal PLLs or external encoder.                                             |

| H               | ADATA[3:0]/GPIO[4:1]                  | 155, 154, 151, 150      | 0                 | PCM Data Out. Eight channels. Serial audio samples relative to BCK                       |

| 1 1             |                                       | 100, 104, 101, 100      |                   | and LRCK. General Purpose I/Os [4:1]                                                     |

| Audio Interface | BCK                                   | 149                     | 0                 | PCM Bit Clock. BCK can be either 48 or 32 times the sampling frequency                   |

| 15              | LRCK                                  | 142                     | ·····             | PCM Left Clock. Identifies the channel for each sample. The polarity is                  |

| te              |                                       | 148                     | 0                 | programma-ble.                                                                           |

|                 | хск                                   | 140                     | 1/0               | Audio External Frequency clock input or output. BCK and LRCK are                         |

| <u> </u>        |                                       | 147                     | 0                 | derived from this clock.                                                                 |

| <b> </b> ¥      | IEC958/GPIO14                         | 156                     | 0                 | PCM data out (IEC-958 format ) or compressed data out                                    |

|                 |                                       | 100                     |                   | (IEC-1937 format). General Purpose I/O [14]                                              |

| $\vdash$        | DAI_DATA/GPIO15                       | 157                     |                   | PCM data input.                                                                          |

|                 |                                       | 157                     | '                 |                                                                                          |

| 드               |                                       | 150                     |                   | General Purpose I/O [15]                                                                 |

| 0               | DAI_BCK/                              | 158                     |                   | PCM input bit clock.                                                                     |

| ≤               | BYPASS_SYSCLK/                        |                         |                   | BYPASS_SYSCLK: Alternate function TBS.                                                   |

| ita             | GPIO16<br>DAI_LRCK/                   |                         | ·····             | General Purpose I/O [16]                                                                 |

| l igil          |                                       | 159                     |                   | PCM left/right clock.                                                                    |

|                 | IEC958BP/GPIO17                       |                         |                   | IEC958 input bypass                                                                      |

|                 |                                       |                         | 1                 | General Purpose I/O [17]                                                                 |

1. I - input, O - output, OD - open drain, PU - requires external pull-up resistor.

#### 2. Pin function

| _            | . Pin function | Pin No. | Type <sup>1</sup> | (4/4) Description                                                              |

|--------------|----------------|---------|-------------------|--------------------------------------------------------------------------------|

|              | IRRX1/GPIO0    | 28      | Туре              | IR Remote Receive. This input connects to an integrated (photo diode,          |

| Ľ            |                | 20      | '                 | band pass. demodulator) IR receiver. General Purpose I/O 0                     |

|              | IDC CL/GPIO18  | 160     | I/O               | Serial clock signal for IDC data transfer. It should be pulled up to the       |

|              |                | 100     | 1/0               | positive supply voltage, depending on the device) using an external            |

| BC           |                |         |                   | pull-up resistor. General Purpose I/O [18]                                     |

| =            | IDC_DA/GPIO19  | 161     |                   | Serial data signal for IDC data transfer. It should be pulled up to the supply |

|              |                |         |                   | voltage using an external pull-up resistor. General Purpose I/O [19]           |

|              | RTS1/GPIO20    | 162     | 0                 | Ready to send, UART1                                                           |

|              |                |         | Ū                 | General Purpose I/O [20]                                                       |

|              | RXD1/GPIO21    | 163     | ·····             | Receive data, UART1                                                            |

| <b>UART1</b> |                |         |                   | General Purpose I/O [21]                                                       |

| AH           | TXD1/GPIO22    | 164     | 0                 | Transmit data, UART1                                                           |

| ∍            |                |         |                   | General Purpose I/O [22]                                                       |

|              | CTS1/GPIO23    | 165     |                   | Clear to send, UART1                                                           |

|              |                |         |                   | General Purpose I/O [23]                                                       |

|              | RTS2/SPI_CLK/  | 185     | 0                 | Ready to send, UART2                                                           |

|              | GPIO37         |         |                   | Serial Peripheral Interface Clock                                              |

|              |                |         |                   | General Purpose I/O [37]                                                       |

|              | RXD2/SPI_MISO/ | 186     | I I               | Receive data, UART2                                                            |

| N            | GPIO38         |         |                   | Serial Peripheral Interface - Master Input/Slave Output                        |

| <b>UART2</b> |                |         |                   | General Purpose I/O [38]                                                       |

| A            | TXD2/SPI_MOSI/ | 187     | 0                 | Transmit data, UART2                                                           |

| _            | GPIO39         |         |                   | Serial Peripheral Interface - Master Output/Slave Input                        |

|              |                |         |                   | General Purpose I/O [39]                                                       |

|              | CTS2/SPI_CS/   | 188     | 1                 | Clear to send, UART2                                                           |

|              | GPIO40         |         |                   | Serial Peripheral Interface ????                                               |

|              |                |         |                   | General Purpose I/O [40]                                                       |

|              | TRST           | 197     |                   | Test reset. BST reset - resets the TAP controller.                             |

|              | . <u></u>      |         |                   | This signal must be pulled low.                                                |

| JTAG         | TDO            | 198     | 0                 | Test data Out. BST serial data output.                                         |

| 5            | TDI/GPI0       | 199     |                   | Test data In. BST serial data chain input.                                     |

|              | The /0 Did     |         |                   | General Purpose Input pin 0.                                                   |

|              | TMS/GPI1       | 200     |                   | Test mode select. Controls state of test access port (TAP) controller.         |

|              | TOK            | 001     |                   | General Purpose Input pin 1.                                                   |

|              | TCK            | 201     |                   | Test clock. Boundary scan test (BST) serial data clock.                        |

1. I - input, O - output, OD - open drain, PU - requires external pull-up resistor.

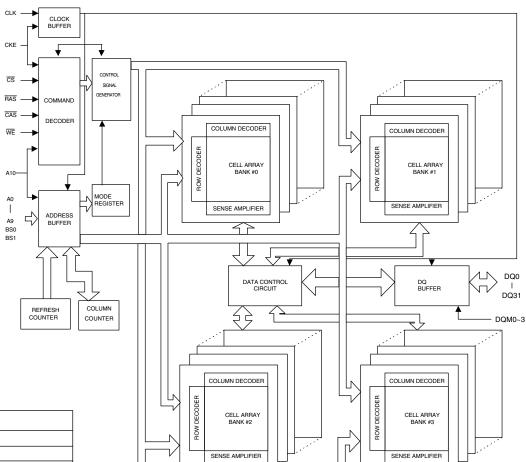

#### 3. Block diagram

#### TH-A5R

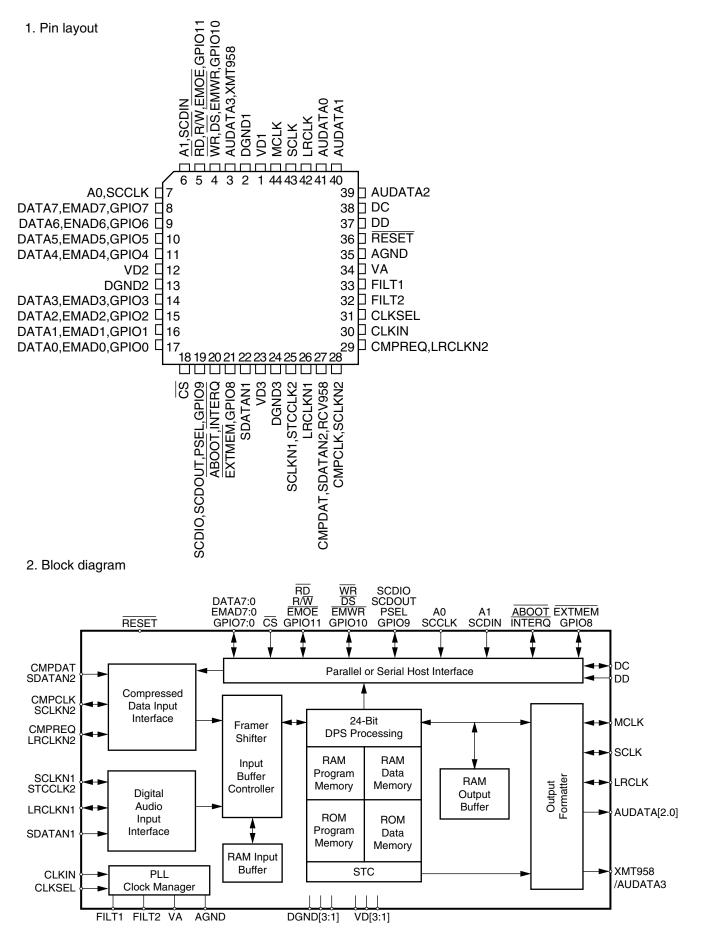

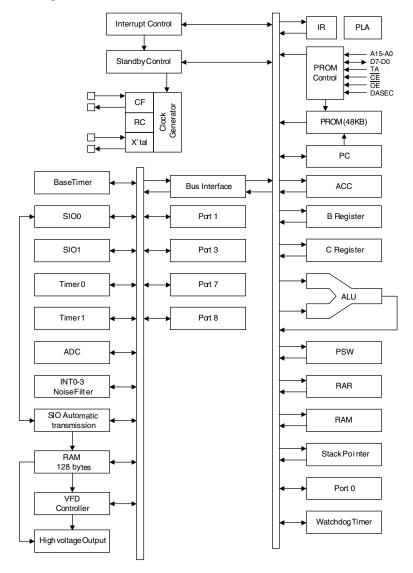

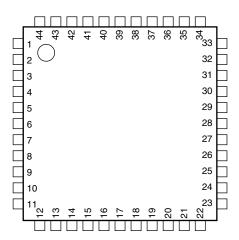

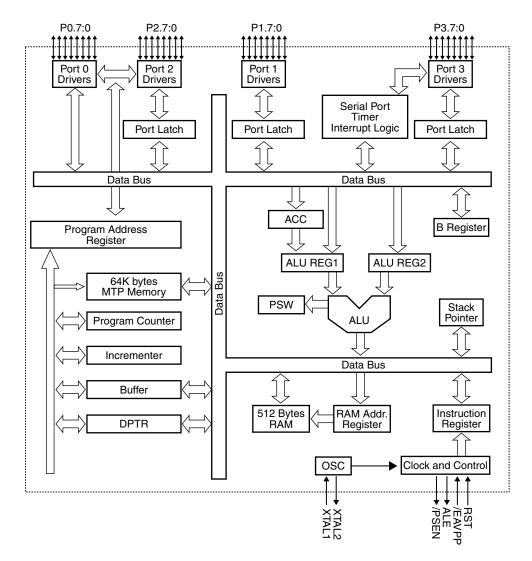

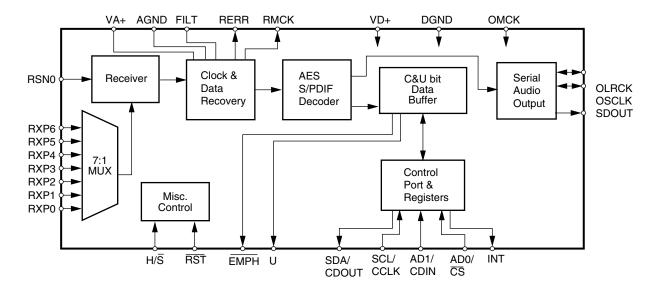

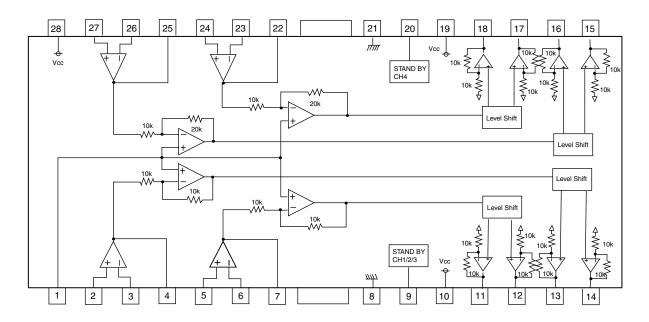

# CS493292 (DIC11) : Audio decoder

#### 3. Pin function

| Pin No. | Symbol                  | Function                                                                   |  |

|---------|-------------------------|----------------------------------------------------------------------------|--|

| 1,12,23 | VD1,VD2,VD3             | Digital Positive Supply                                                    |  |

| 2,13,24 | DGND1,DGND2,DGND3       | Digital Supply Ground                                                      |  |

| 3       | AUDATA3,XMT958          | SPDIF Transmitter Output, Digital Audio Output 3                           |  |

| 4       | WR,DS,EMWR,GPIO10       | Host write strobe or Host data strobe or External Memory write enable or   |  |

|         |                         | General purpose input& output Number 10                                    |  |

| 5       | RD,R/W,EMOE,GPIO11      | Host Parallel Output Enable or Host Parallel R/W or External Memory Output |  |

|         |                         | Enable or General Purpose Input & Output Number11                          |  |

| 6       | A1,SCDIN                | Host Address Bit One or SPI Serial Control Data Input                      |  |

| 7       | A0,SCCLK                | Host Parallel Address Bit Zero or Serial Control Port Clock                |  |

| 8       | DATA7, EMAD7, GPIO7     | Data Bus                                                                   |  |

| 9       | DATA6,ENAD6,GPIO6       | Data Bus                                                                   |  |

| 10      | DATA5, EMAD5, GPIO5     | Data Bus                                                                   |  |

| 11      | DATA4,EMAD4,GPIO4       | Data Bus                                                                   |  |

| 14      | DATA3,EMAD3,GPIO3       | Data Bus                                                                   |  |

| 15      | DATA2, EMAD2, GPIO2     | Data Bus                                                                   |  |

| 16      | DATA1,EMAD1,GPIO1       | Data Bus                                                                   |  |

| 17      | DATA0,EMAD0,GPIO0       | Data Bus                                                                   |  |

| 18      | CS                      | Host Parallel Chip Select, Host Serial SPI Chip Select                     |  |

| 19      | SCDIO,SCDOUT,PSEL,GPIO9 | Serial Control Port Data Input and Output, Parallel Port Type Select       |  |

| 20      | ABOOT,INTERQ            | Control Port Interrupt Request, Automatic Boot Enable                      |  |

| 21      | EXTMEM,GPIO8            | External Memory Chip Select or General Purpose Input & Output Number 8     |  |

| 22      | SDATAN1                 | PCM Audio Data Input Number One                                            |  |

| 25      | SCLKN1,STCCLK2          | PCM Audio Input Bit Clock                                                  |  |

| 26      | LRCLKN1                 | PCM Audio Input Sample Rata Clock                                          |  |

| 27      | CMPDAT,SDATAN2          | PCM Audio Data Input Number Tow                                            |  |

| 28      | CMPCLK,SCLKN2           | PCM Audio Input bit Clock                                                  |  |

| 29      | CMPREQ,LRCLKM2          | PCM Audio Input Sample Rate Clock                                          |  |

| 30      | CLKIN                   | Master Clock Input                                                         |  |

| 31      | CLKSEL                  | DSP Clock Select                                                           |  |

| 32      | FILT1                   | Phase Locked Loop Filter                                                   |  |

| 33      | TILT2                   | Phase-Locked Loop Filter                                                   |  |

| 34      | VA                      | Analog Positive Supply                                                     |  |

| 35      | AGND                    | Analog Supply Ground                                                       |  |

| 36      | RESET                   | Master Reset Input                                                         |  |

| 37      | DC                      | Reserved                                                                   |  |

| 38      | DD                      | Reserved                                                                   |  |

| 39      | AUDATA2                 | Digital Audio Output 2                                                     |  |

| 40      | AUDATA1                 | Digital Audio Output 1                                                     |  |

| 41      | AUDATAO                 | Digital Audio Output 0                                                     |  |

| 42      | LRCLK                   | Audio Output Sample Rate Clock                                             |  |

| 43      | SCLK                    | Audio Output Bit Clock                                                     |  |

| 44      | MCLK                    | Audio Master Clock                                                         |  |

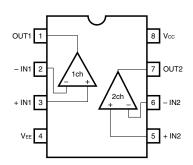

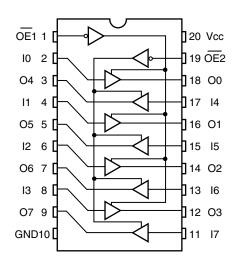

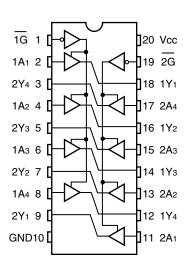

■ BA4560 (IC2, IC5, IC6, IC7, CIC11, CIC13, FIC2, FIC4, FIC5, FIC6, FIC11, RIC11, RIC13) : Dual op amp.

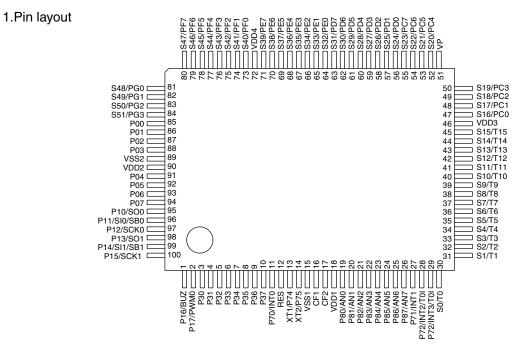

1.Pin layout

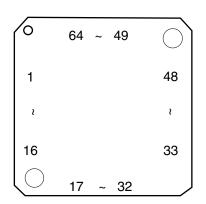

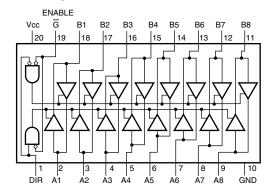

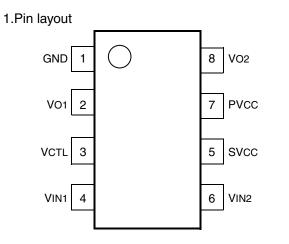

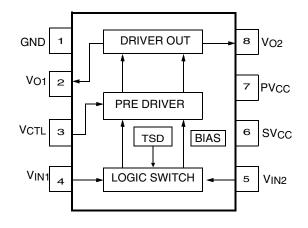

# SP3721A (U7) : DVD driver

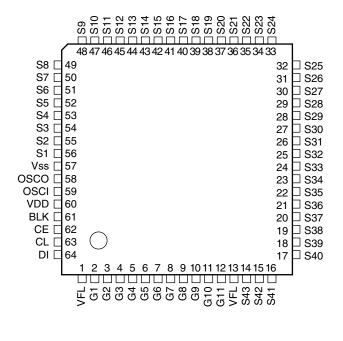

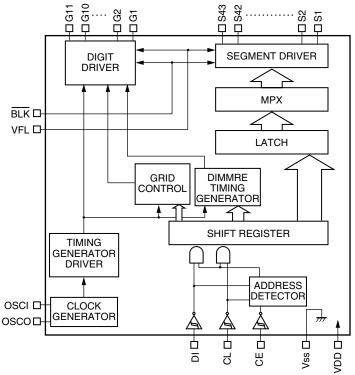

1.Pin layout

#### 2.Pin function

(1/2)

| Pin No. | Symbol  | I/O | Function                                                                               |

|---------|---------|-----|----------------------------------------------------------------------------------------|

| 1       | DVDRFP  | I   | RF Signal Inputs. Differential RF signal attenuator input pins.                        |

| 2       | DVDRFN  |     |                                                                                        |

| 3,4     | PD1,PD2 | I   | CD Photo detector Interface Inputs. Inputs from the CD photo detector error outputs.   |

| 5~6     | A2,B2   | I   | Photo Detector Interface Inputs. AC coupled inputs for the DPD from                    |

| 7~ 8    | C2,D2   |     | the main beam Photo detector matrix outputs.                                           |

| 9       | CP      | I/O | Differential Phase tracking LPF pin. An external capacitance is                        |

|         |         |     | connected between this pin and the CN pin.                                             |

| 10      | CN      | I/O | Differential Phase tracking LPF pin. An external capacitance is                        |

|         |         |     | connected between this pin and the CP pin.                                             |

| 11~14   | A,B,C,D | I   | Photo Detector Interface Inputs. Inputs from the main beam Photo                       |

|         |         |     | detector matrix outputs.                                                               |

| 15~16   | E,F     | I   | CD tracking Error Inputs. Inputs from the CD photo detector error outputs.             |

| 17      | CDTE    | -   | CD Tracking. E-F Opamp output for feedback.                                            |

| 18      | VCI2    | -   | Reference Voltage input. DC bias voltage input for the servo input reference.          |

| 19      | NC      | -   | No Connect.                                                                            |

| 20      | VNB     | -   | Ground. Ground pin for the servo block.                                                |

| 21      | DVDPD   | I   | APC Input. DVD APC input pin from the monitor photo diode.                             |

| 22      | DVDLD   | 0   | APC output. DVD APC output pin to control the laser power.                             |

| 23      | CDPD    | I   | APC Input. DVD APC input pin from the monitor photo diode.                             |

| 24      | CDLD    | 0   | APC output. DVD APC output pin to control the laser power.                             |

| 25      | LDON#   | I   | APC output. on/off. APC output control pin. A low level activates the                  |

|         |         |     | LD output. (open high)                                                                 |

| 26      | VC      | -   | Reference Voltage output. This pin provides the internal DC bias                       |

|         |         |     | reference voltage (+2.5+ fix). Output impedance is less than 50 ohms.                  |

| 27      | VCI     | -   | Reference Voltage input. DC bias voltage input for the servo input reference.          |

| 28      | VPB     | -   | Power. Power supply pin for the servo block.                                           |

| 29      | MIRR    | 0   | Mirror Detect Output. Mirror Detect comparator output. Pseudo CMOS output.             |

| 30      | MP      | -   | MIRR signal Peak hold pin. An external capacitance is connected to                     |

|         |         |     | between this pin and VPB.                                                              |

| 31      | MB      | -   | MIRR signal Bottom hold pin. An external capacitance is connected to                   |

|         |         |     | between this pin and VPB.                                                              |

| 32      | FDCHG#  | I   | Low Impedance Enable. A TTL compatible input pin that activates the FDCHG switches.    |

|         |         |     | A low level activates the switches and the falling edge of the internal FDCHG triggers |

|         |         |     | the fast decay for the NIRR bottom hold circuit. (open high)                           |

| 33      | MLPF    | -   | MIRR signal LPF pin. An external capacitance is connected between this pin and VPB.    |

| 2.Pin   | function |     | (2/2)                                                                                                                                                                                                       |

|---------|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No. | Symbol   | I/O | Function                                                                                                                                                                                                    |

| 34      | MEVO     | 0   | SIGO Bottom Envelope Output. Bottom envelope for Mirror detection.                                                                                                                                          |

| 35      | MIN      | I   | RF signal Input for Mirror. AC coupled inputs for the mirror detection circuit from the pull-in signal output. (PI)                                                                                         |

| 36      | PI       | 0   | Pull-in Signal Output. The summing signal output of A,B,C,D or PD1,<br>PD2 for mirror detection. Reference to VCI.                                                                                          |

| 37      | DFT      | 0   | Defect Output. Pseudo CMOS output. When a defect is detected, the DFT output goes high. Also the servo AGC output can be monitored at this pin, When CAR bits 7-4 are '0011'.                               |

| 38      | TPH      |     | PI Top Hold pin. An external capacitance is connected between this pin and VPB.                                                                                                                             |

| 39      | MEV      | -   | SIGO Bottom Envelope pin. An external capacitance is connected between this pin and VPB.                                                                                                                    |

| 40      | MEI      | 1   | Mirror Envelope Input. The SIGO envelope input pin.                                                                                                                                                         |

| 41      | TE       | 0   | Tracking Error Signal Output. Tracking error output reference to VCI.                                                                                                                                       |

| 42      | FE       | 0   | Focusing Error Signal Output. Focus error output reference to VCI.                                                                                                                                          |

| 43      | CE       | 0   | Center Error Signal Output. Center error out put reference to VCI.                                                                                                                                          |

| 44      | LCN      | -   | Center Error LPF pin. An external capacitance is connected between<br>this pin and the LCP pin.                                                                                                             |

| 45      | LCP      | -   | Center Error LPF pin. An external capacitance is connected between<br>this pin and the LCN pin.                                                                                                             |

| 46      | SCLK     | I   | Serial Clock. Serial Clock CMOS input. The clock applied to this pin<br>is synchronized with the data applied to SDATA. (Not to be left open).                                                              |

| 47      | SDATA    | I/O | Serial Data. Serial data bi-directional CMOS pin. NRZ programming                                                                                                                                           |

| 77      | JUAIA    | 1/0 | data for the internal registers is applied to this input. (Not to be left open)                                                                                                                             |

| 48      | SDEN     | 1   | Serial Data Enable. Serial enable CMOS input. A high level input                                                                                                                                            |

|         | 002.1    |     | enables the serial port. (Not to be left open)                                                                                                                                                              |

| 49      | HOLD1    | I   | Hold Control. ATTL compatible control pin which, when pulled high, disables the RF AFC charge pump and holds the RE AGC amplifier gain at its present value. (open high)                                    |

| 50      | VNA      | -   | Ground. Ground pin for the RF block and serial port.                                                                                                                                                        |

| 51      | FNN      | 0   | Differential Normal Output. Filter normal outputs.                                                                                                                                                          |

| 52      | FNP      | 0   | Differential Normal Output. Filter normal outputs.                                                                                                                                                          |

| 53      | DIP      | 1   | Analog inputs for RF Single Buffer. Differential analog inputs to the RF single-ended output buffer and full wave rectifier.                                                                                |